### EE 435

Lecture 24

**Data Converter Operation**

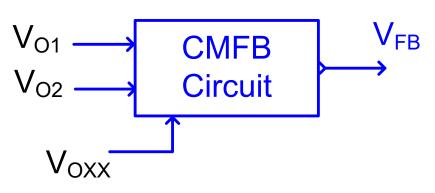

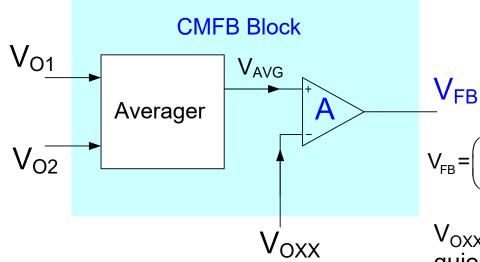

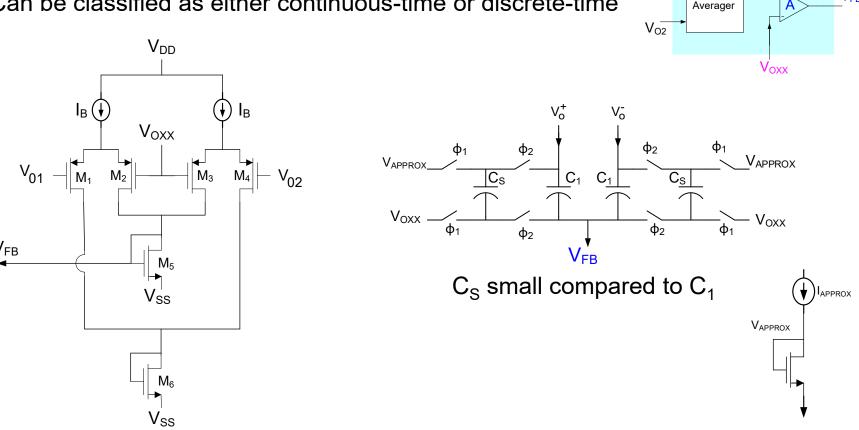

### Basic Operation of CMFB Block

$$V_{FB} = \left(\frac{V_{01} + V_{02}}{2}\right) A(s)$$

V<sub>OXX</sub> is the desired quiescent voltage at the stabilization node (irrespective of where V<sub>FB</sub> goes) • • • • Review from last lecture .• • • •

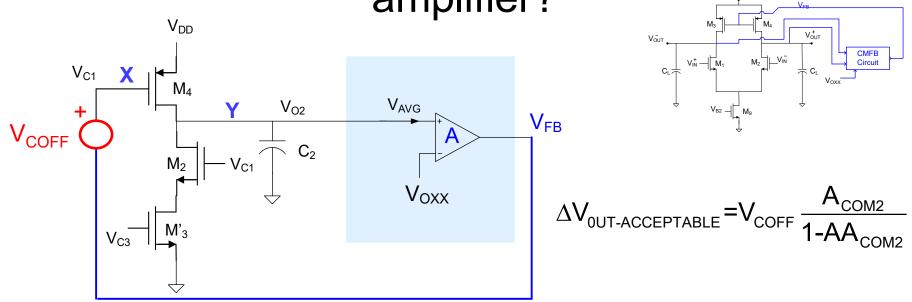

How much gain is needed in the CMFB amplifier?

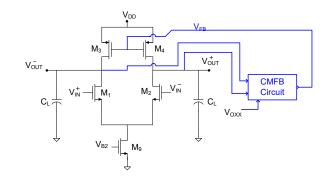

#### The CMFB Loop

- This does not require a particularly large gain

- This is the loop that must be compensated since A and A<sub>COMP2</sub> will be frequency dependent

- Miller compensation capacitor for compensation of differential loop will often appear in shunt with C<sub>2</sub>

- Can create this "half-circuit" loop (without CM inputs on a fully differential structure) for simulations

- Results extend readily to two-stage structures with no big surprises

- Capacitances on nodes X and Y create poles for CMFB circuit

- Reasonably high closed-loop CMFB bandwidth needed to minimize shifts in output due to high-frequency common-mode noise

#### **Review from last lecture**

$V_{FB}$

### CMFB Circuits

- Several (but not too many) CMFB blocks are widely used

- Can be classified as either continuous-time or discrete-time

- V<sub>OXX</sub> generated by simple bias generator

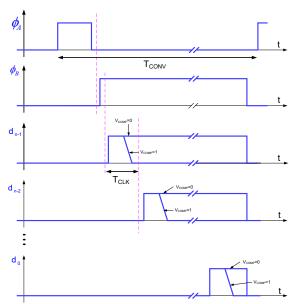

- $\varphi_1$  and  $\varphi_2$  are complimentary non-overlapping clocks that run continuously

### **Data Converters**

### **Types:**

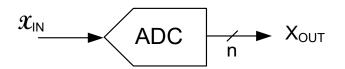

A/D (Analog to Digital)

Converts Analog Input to a Digital Output

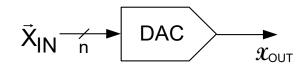

D/A (Digital to Analog)

Converts a Digital Input to an Analog Output

A/D is the world's most widely used mixed-signal component

D/A is often included in a FB path of an A/D

A/D and D/A fields will remain hot indefinitely technology advances make data converter design more challenging embedded applications designs often very application dependent

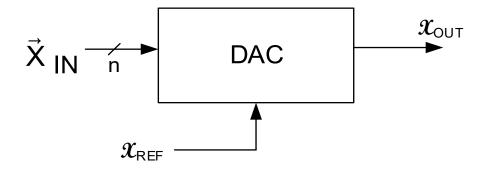

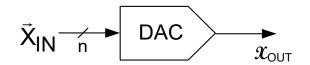

### D/A Converters

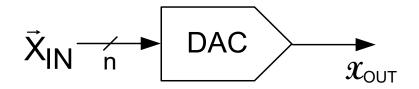

Basic structure:

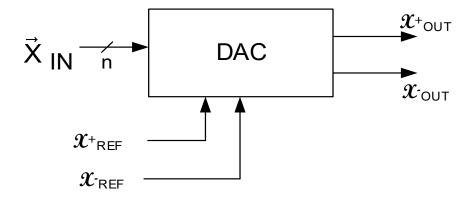

Basic structure with differential outputs::

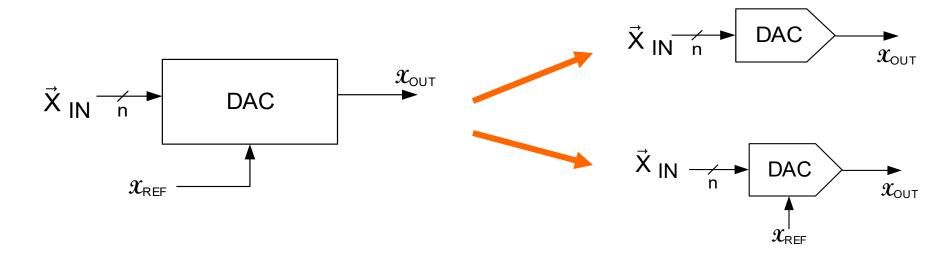

### D/A Converters

Notation:

$\mathscr{X}_{\mathsf{REF}}$  is always present though often not shown on the symbol for the DAC

### D/A Converters

$$\vec{X}_{IN} = \langle b_{n-1}, b_{n-1}, ..., b_1, b_0 \rangle$$

b<sub>0</sub> is the Least Significant Bit (LSB)

b<sub>n-1</sub> is the Most Significant Bit (MSB)

Number of ideal DAC outputs: N=2<sup>n</sup>

Note: some authors use different index notation

An Ideal DAC is characterized at low frequencies by its static performance

$$\vec{X}$$

IN  $\vec{n}$  DAC  $\mathcal{X}_{OUT}$

$$\vec{X}_{IN} = \langle b_{n-1}, b_{n-1}, ..., b_1, b_0 \rangle$$

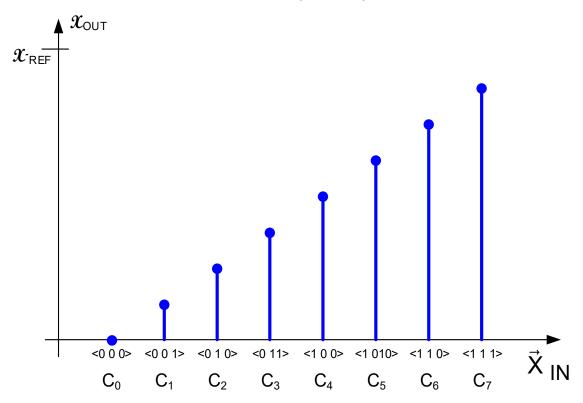

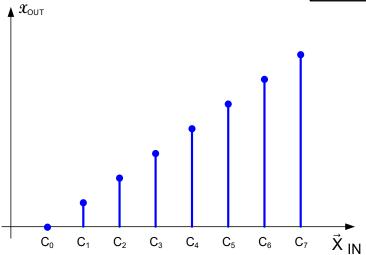

An Ideal DAC transfer characteristic (3-bits)

Code C<sub>k</sub> is used to represent the decimal equivalent of the binary number <br/>

b<sub>n-1</sub> .. b<sub>0</sub>)>

$$\vec{X}_{1N} = \langle b_{n-1}, b_{n-1}, ..., b_1, b_0 \rangle$$

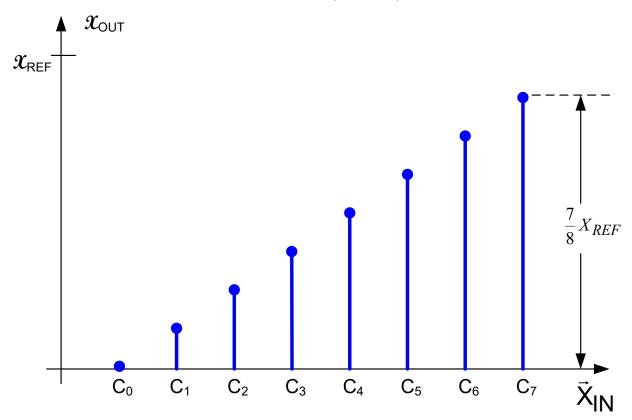

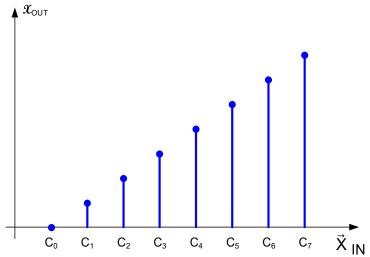

An Ideal DAC transfer characteristic (3-bits)

$$\vec{X}$$

IN n DAC  $x_{OUT}$

$$\vec{X}_{1N} = \langle b_{n-1}, b_{n-1}, ..., b_1, b_0 \rangle$$

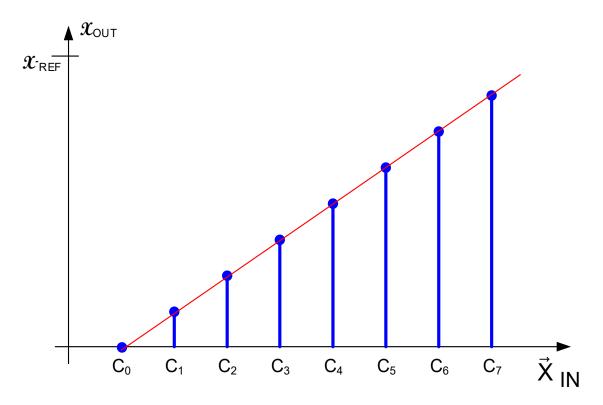

An Ideal DAC transfer characteristic (3-bits)

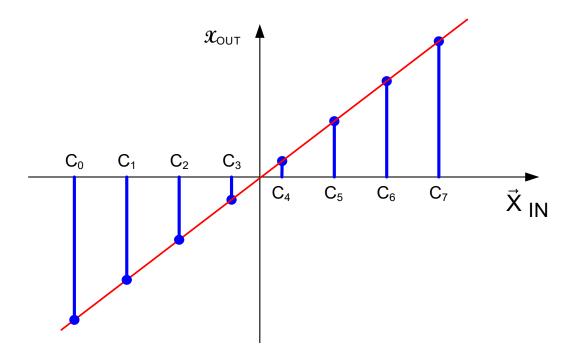

All points of this ideal DAC lie on a straight line

- Most D/A ideally have a linear relationship between binary input and analog output

- Output represents a discrete set of continuous variables

- Typically this number is an integral power of 2, i.e. N=2<sup>n</sup>

- $\vec{X}_{IN}$  is always dimensionless

- $\mathcal{X}_{\mathsf{OUT}}$  could have many different dimensions

- An ideal nonlinear characteristic is also possible (waveform generation and companding)

- Will assume a linear transfer characteristic is desired unless specifically stated to the contrary

$$\vec{X}$$

IN n DAC  $\mathcal{X}_{OUT}$

For this ideal DAC

$$\mathcal{X}_{OUT} = X_{REF} \left( \frac{b_{n-1}}{2} + \frac{b_{n-2}}{4} + \frac{b_{n-3}}{8} + ... + \frac{b_1}{2^{n-1}} + \frac{b_0}{2^n} \right)$$

$$\mathcal{X}_{OUT} = X_{REF} \sum_{j=1}^{n} \frac{b_{n-j}}{2^j}$$

- Number of outputs gets very large for n large

- Spacing between outputs is X<sub>RFF</sub>/2<sup>n</sup> and gets very small for n large

- Ideal steps all equal and termed the LSB

- $\mathcal{X}_{\mathsf{LSB}}$  gets very small for small  $\mathcal{X}_{\mathsf{REF}}$  and large n

e.g. If  $\mathcal{X}_{REF}$ =1V and n=16, then N=2<sup>16</sup>=65,536,  $\mathcal{X}_{LSB}$ =15.25 $\mu$ V

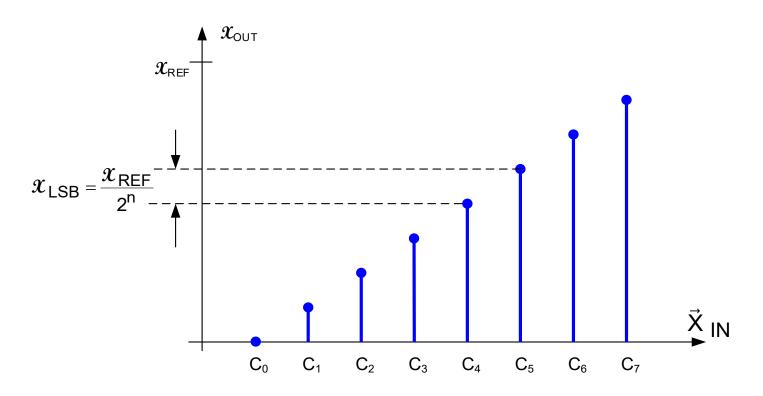

An alternate ideal 3-bit DAC

Irrespective of which form is considered, the increment in the output for one Boolean bit change in the input is  $\mathcal{X}_{\text{LSB}}$  and the total range is 1LSB less than  $\mathcal{X}_{\text{REF}}$

## Applications of DACs

- Waveform Generation

- Voltage Generation

- Analog Trim or Calibration

- Industrial Control Systems

- Feedback Element in ADCs

- •

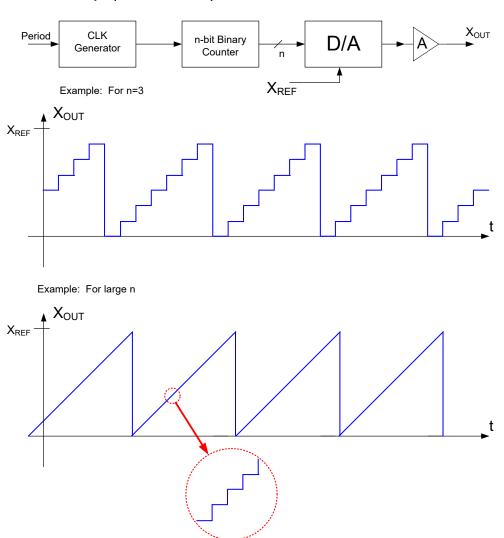

### Waveform Generation with DACs

#### Ramp (Saw-tooth) Generator

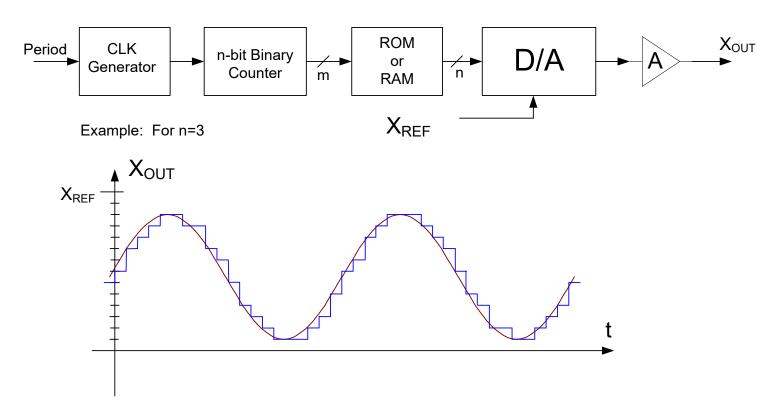

### Waveform Generation with DACs

#### Sine Wave Generator

Distortion of the desired waveforms occurs due to both time and amplitude quantization

Often a filter precedes or follows the buffer amplifier to smooth the output waveform

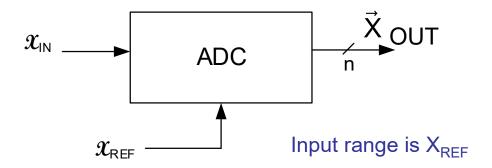

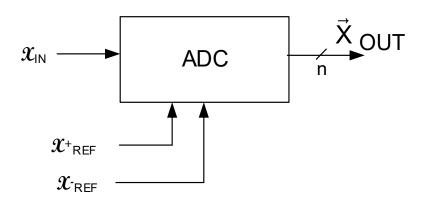

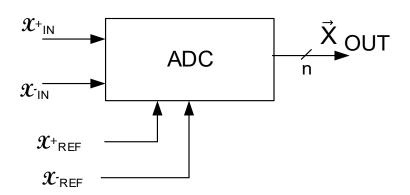

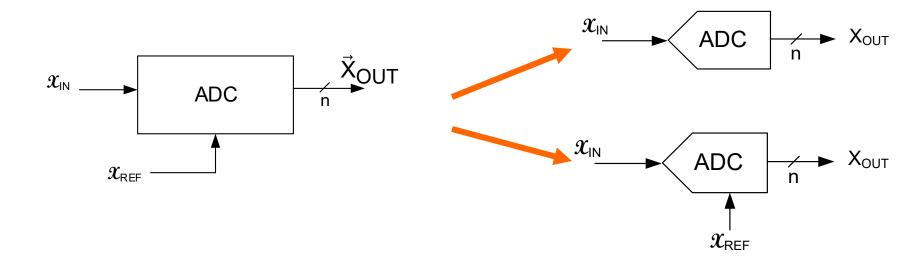

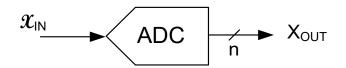

Basic structure:

Basic structure with differential inputs/references:

Input range is  $X^{+}_{REF}$  -  $X^{-}_{REF}$

Input range is  $2(X^{+}_{REF} - X^{-}_{REF})$

#### Notation:

$$\vec{X}_{OUT} = < d_{n-1}, d_{n-2}, ...d_0 >$$

d<sub>0</sub> is the Least Significant Bit (LSB)

d<sub>n-1</sub> is the Most Significant Bit (MSB)

Number of ideal ADC outputs: N=2<sup>n</sup>

Note: some authors use different index notation

An Ideal ADC is characterized at low frequencies by its static performance

$X_{IN}$  ADC n  $X_{OUT}$

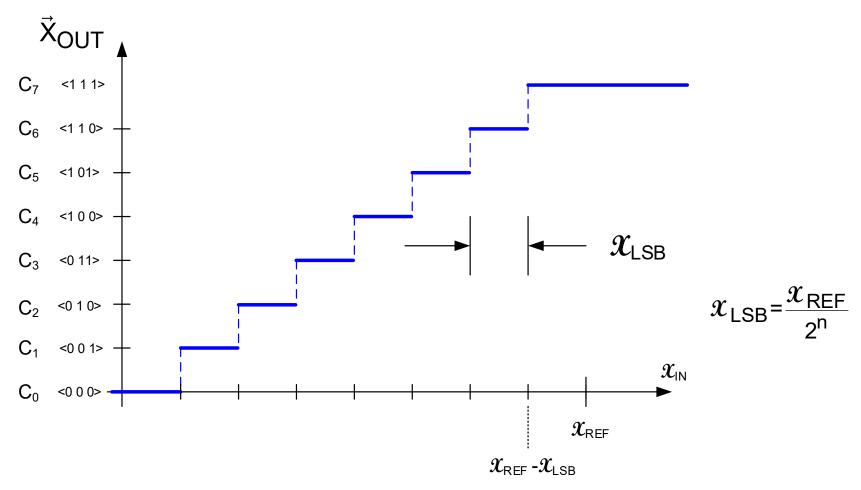

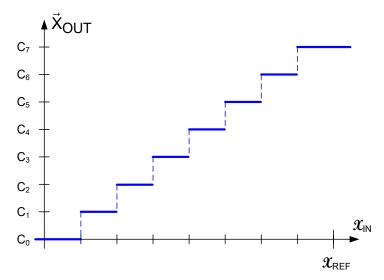

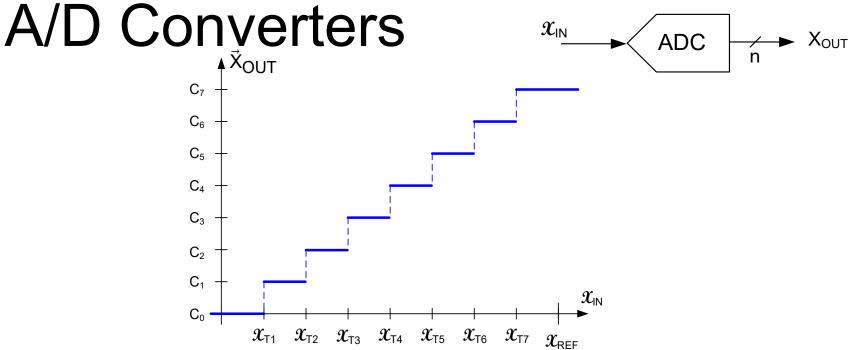

An Ideal ADC transfer characteristic (3-bits)

$$\vec{X}_{OUT} = < d_{n-1}, d_{n-2}, ...d_0 >$$

$X_{IN}$  ADC n  $X_{OUT}$

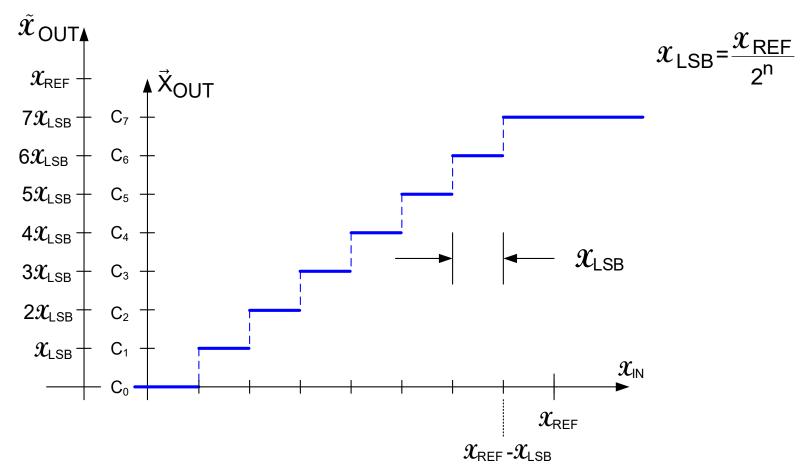

An Ideal ADC transfer characteristic (3-bits)

$$\vec{X}_{OUT} = < d_{n-1}, d_{n-2}, ...d_0 >$$

The second vertical axis, labeled  $\mathcal{ ilde{X}}_{OUT}$  ,is the interpreted value of  $\vec{x}_{OUT}$

For this ideal ADC

$$\mathcal{X}_{REF}\left(\frac{d_{n-1}}{2} + \frac{d_{n-2}}{4} + \frac{d_{n-3}}{8} + \dots + \frac{d_1}{2^{n-1}} + \frac{d_0}{2^n}\right) = \mathcal{X}_{IN} + \epsilon$$

where  $\varepsilon$  is small (typically less than 1LSB)

$$\mathcal{X}_{REF} \sum_{j=1}^{n} \frac{d_{n-j}}{2^j} = \mathcal{X}_{IN} + \varepsilon$$

- Number of bins gets very large for n large

- Spacing between break points is  $\mathcal{X}_{REF}/2^n$  and gets very small for n large  $\epsilon$  is the **quantization error** and is inherent in any ADC

#### **Transition Points**

- Actual values of  $\mathcal{X}_{\mathsf{IN}}$  where transitions occur are termed <u>transition points</u> or <u>break points</u>

- For an ideal n-bit ADC, there are 2<sup>n</sup>-1 transition points

- Ideally the transition points are all separated by 1 LSB  $-X_{LSB}=X_{REF}/2^n$

- Ideally the transition points are uniformly spaced

- In an actual ADC, the transition points will deviate a little from their ideal location Labeling Convention:

We will define the transition point  $X_{Tk}$  to be the break point where the transition in the code output to code  $C_k$  occurs. This seemingly obvious ordering of break points becomes ambiguous, though, when more than one break points cause a transition to code  $C_k$  which can occur in some nonideal ADCs

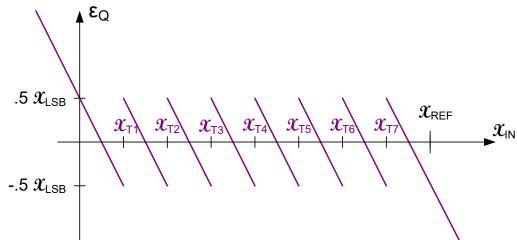

# A/D Converters $oldsymbol{\mathcal{X}}_{\mathsf{IN}}$ **Quantization Errors** $\mathcal{X}_{T1} = \mathcal{X}_{LSB}$ $C_5$ $x_{\text{LSB}}$ $2x_{\text{LSB}}$ $3x_{\text{LSB}}$ $4x_{\text{LSB}}$ $5x_{\text{LSB}}$ $6x_{\text{LSB}}$ $7x_{\text{LSB}}$ $x_{\text{LSB}}$

Magnitude of  $\epsilon_Q$  bounded by  $\mathcal{X}_{LSB}$  for an ideal A/D

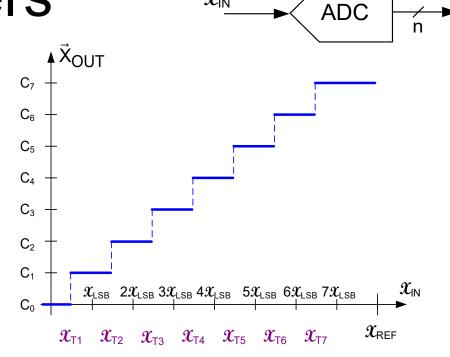

**Quantization Errors**

**Another Ideal ADC**

$$\mathcal{X}_{T1} = \mathcal{X}_{LSB}/2$$

${oldsymbol{\mathcal{X}}_{\mathsf{IN}}}$

$$\varepsilon_Q = \tilde{\mathcal{X}}_{OUT} - \mathcal{X}_{IN}$$

Magnitude of  $\epsilon_{\rm Q}$  bounded by ½  $\mathcal{X}_{\rm LSB}$

Is the performance of this ideal ADC really better than that of the previous ideal ADC?

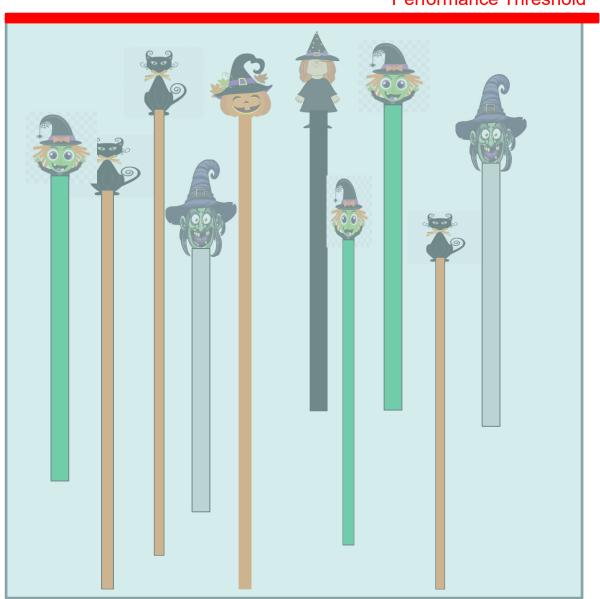

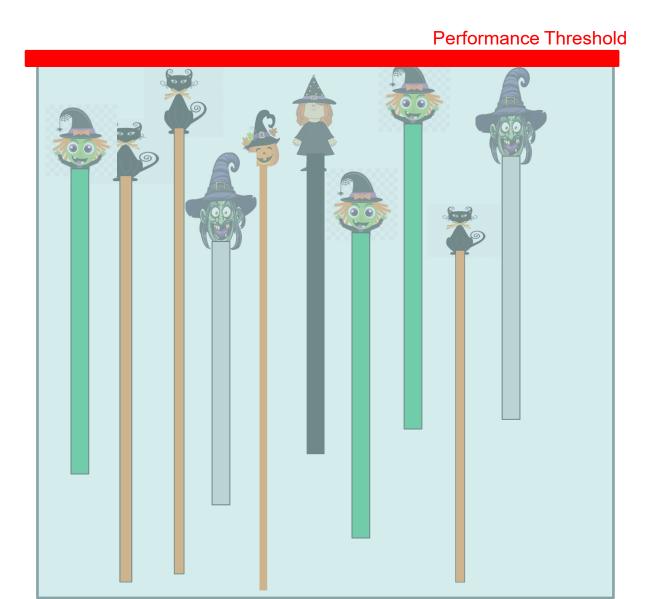

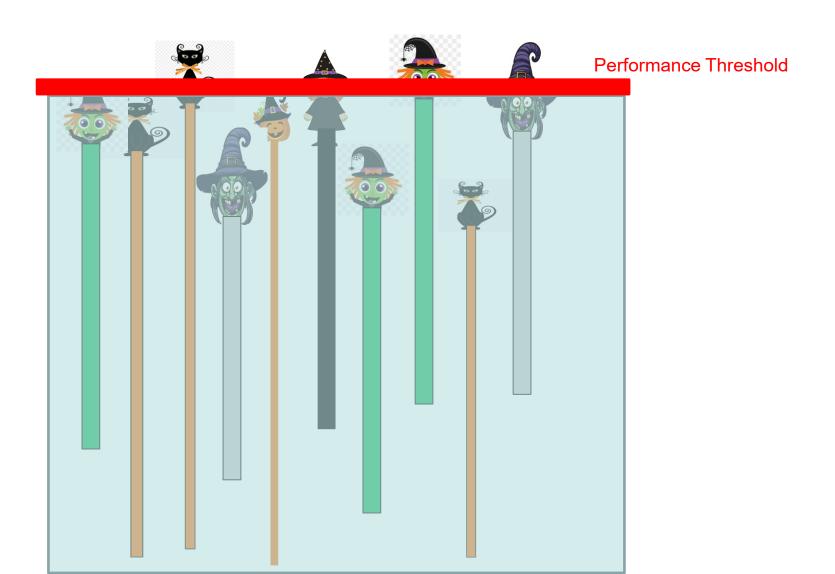

- Large number of different circuits have been proposed for building data converters

- Often a dramatic difference in <u>performance</u> from one structure to another

- Performance of almost all structures are identical if ideal components are used

- Much of data converter design involves identifying the problems associated with a given structure and figuring out ways to reduce the effects of these problems

- Critical that all problems that are significant be identified and solved

- Many of the problems are statistical in nature and implications of not solving problems are in a yield loss that may be dramatic

Ideally all performance limitations below performance threshold

Performance Threshold

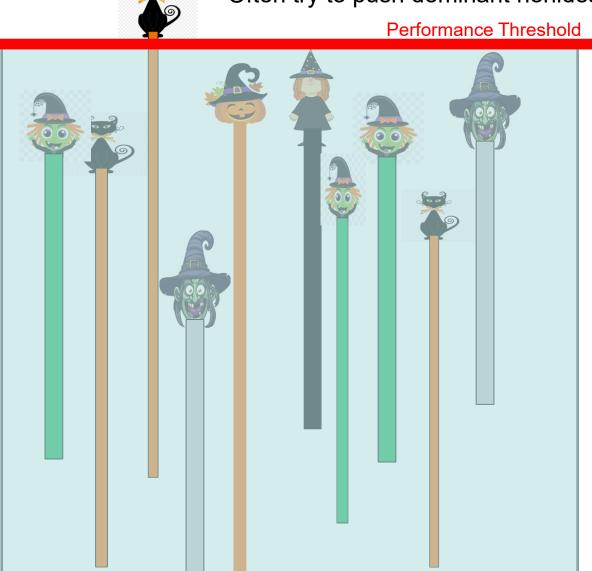

Often one or two nonideal effects above performance threshold

Often try to push dominant nonideal effect down

Often one or two nonideal effects above performance threshold

Often try to push dominant nonideal effect down

If performance threshold is made "higher", other effects pop up as dominant

#### Push them down too

Ultimately enhancing performance threshold makes it more difficult to further improve performance

#### Strategy for discussing data converters

- Briefly look at some different data converter architectures

- Detailed discussion of performance parameters for data converters

- More detailed discussion of data converter architectures

#### **Nyquist Rate**

Flash

Charge Redistribution

**Pipeline**

Two-step and Multi-Step

Interpolating

Algorithmic/Cyclic

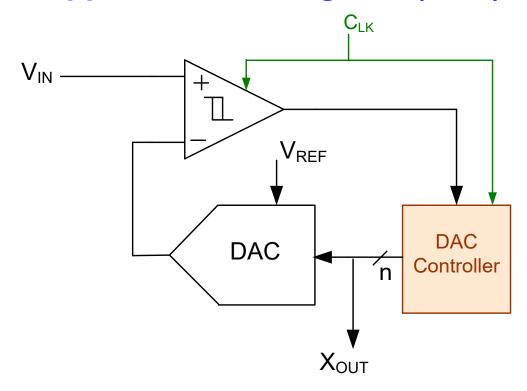

Successive Approximation (Register) SAR

Single Slope / Dual Slope

Subranging

Folded

Interleaved

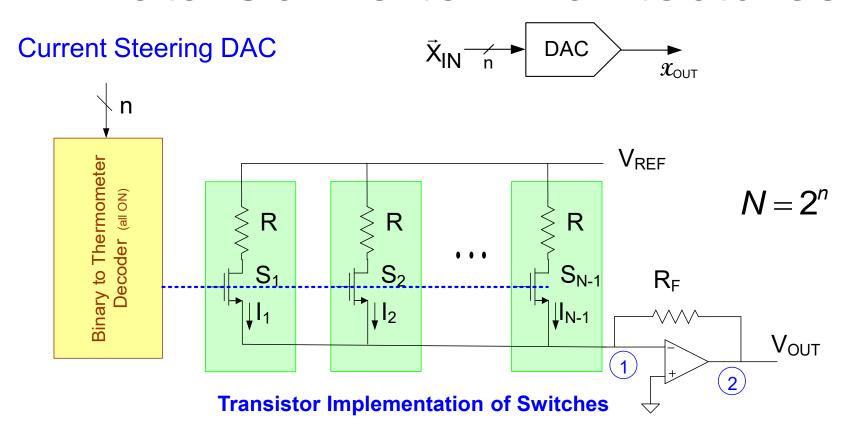

**Current Steering**

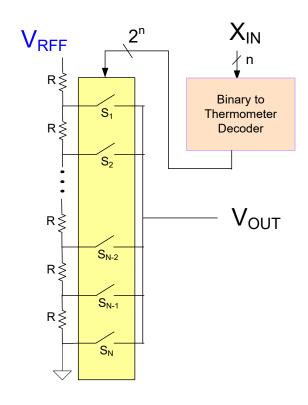

R-string

Charge Redistribution

Algorithmic

R-2R (ladder)

**Pipelined**

Subranging

#### Over-Sampled (Delta-Sigma)

Discrete-time

First-order/Higher Order

Continuous-time

Discrete-time

First-order/Higher Order

Continuous-time

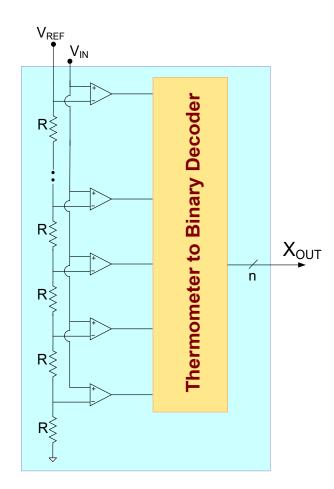

R-String DAC

**Basic R-String DAC including Logic to Control Switches**

Assume k switches are on 0<k<N-1 as determined by digital input code

#### **Flash**

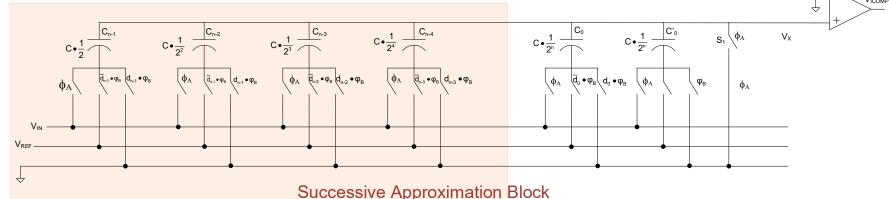

#### **Successive Approximation Register (SAR)**

**Charge Redistribution**

#### Redistribute charge with switches to drive Vx to 0

$$Q_{SAM} = V_{IN} \left( \sum_{i=0}^{n-1} C_i + \left[ C_0' \right] \right) = V_{IN} \left( \sum_{i=0}^{n-1} \frac{C}{2^{n-i}} + \left[ \frac{C}{2^n} \right] \right) = V_{IN} C$$

$$Q_{REDIS} = V_{REF} \sum_{i=0}^{n-1} d_i \frac{C}{2^{n-i}}$$

$$Q_{SAM} = Q_{REDIS}$$

$$V_{REF} \sum_{i=0}^{n-1} d_i \frac{C}{2^{n-i}} = V_{IN} C$$

$$V_{IN} = V_{REF} \sum_{i=0}^{n-1} \frac{d_i}{2^{n-i}}$$

Stay Safe and Stay Healthy!

### End of Lecture 24